SATELLITE PROCESSORS: THE SKY'S THE LIMIT

# The COTS Technology Authority EMBEDDED SYSTEMS VOLUME 3 NUMBER 4 JULY/AUG 2007

IN THIS ISSUE:

#### Chris A. Ciufo

What's up with the market?

#### **Don Dinaee**

SWEPT up for real?

#### **Duncan Young**

Inside Ethernet switch code

#### **Guest opinion**

Software for the long term

Industry

Security

Military

Game Console

# Storage Leader

Coming Soon!

- . SATA Interface

- . Ultra DMA Support

- . No Seek Error & No Noise

- . Lower Power Consumption

- . No Latency Delay

- . Shock Resistant & Anti-vibration

- . RoHS Compliant

PQI Corporation Tel:(510)651-7281 Fax:(510)651-7240

Learn more at: www.pqimemory.com

# Synplify® DSP ASIC Edition

# A Breakthrough in DSP Design

Synplicity's Synplify DSP synthesis solution offers a fast, efficient way to implement DSP algorithms in silicon. By automating architectural optimizations like pipelining, resource sharing, and multi-channelization, engineers can save months of RTL coding, simplify design capture, speed up verification, and create technology-independent IP.

#### Symplify DSP Software Uniquely Offers:

- Technology-independent DSP modeling library

- Comprehensive multi-rate and vector math support

- Fixed-point quantization and analysis tools

- Powerful DSP synthesis engine

- Architecturally optimized Verilog and **VHDL** implementation

- Target the latest ASIC technologies and **FPGA** devices

- Integrated support for standard ASIC design flows

- Memory extraction for flexible support of 3rd party memory vendors

For more information on Synplicity's Synplify DSP solution and all of Synplicity's offerings, please visit our website at www.synplicity.com or contact info@synplicity.com

# Vilitary EMBEDDED SYSTEMS

July/August Volume 3 Number 4

#### **COLUMNS**

#### **Industry Analysis**

7 SWEPT up for real?

By Don Dingee

#### Field Intelligence

8 Inside Ethernet switch source code By Duncan Young

#### **Guest Opinion**

10 Developing defense software systems for the long term

By Gary Cato, Aonix

#### **Crosshairs Editorial**

46 What's up with the market? Perceptions, rather than reality, are adversely affecting the embedded COTS market

By Chris A. Ciufo

# **FEATURES**

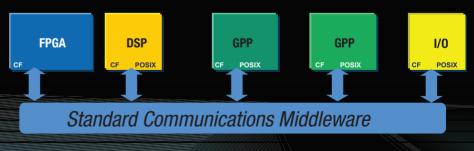

#### Trends in SDR and reconfigurable computing

12 Next-generation SDR operating environment takes on SWaP challenges in resourceconstrained platforms

By Dominick Paniscotti and Jerry Bickle, PrismTech Corporation

#### 16 FPGAs: Solving future proofing in military applications via technology insertion

By Mark Littlefield, Curtiss-Wright Controls Embedded Computing, and Manuel Uhm, Xilinx, Inc.

#### 20 Configurable PMCs put an FPGA to work

By Jeff Biviano and Dave Barker, VMETRO, Inc.

#### When safety and security converge

26 Hardware-based solution aides: Design assurance for airborne systems

By Irene Sysenko, PhD, Aldec, Inc., and Ravi Pragasam, Actel Corporation

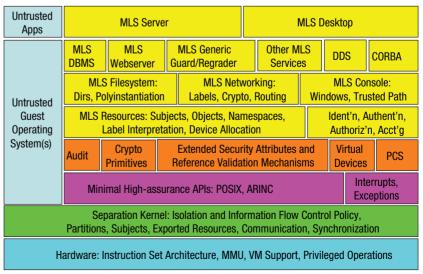

30 MILS: Protecting our most vital systems

By Rance J. DeLong, LynuxWorks, Inc.

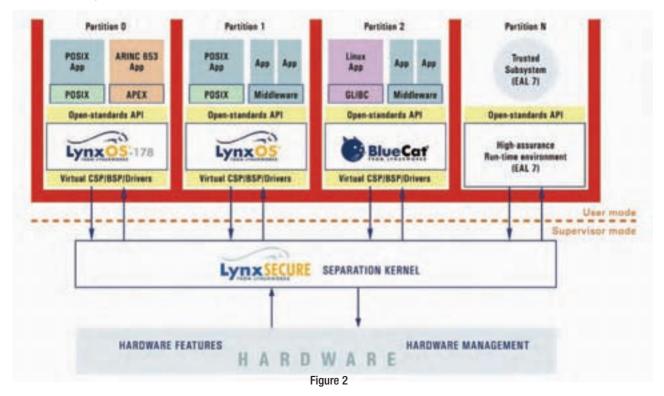

36 Multilevel security in tightly coupled military systems: Virtualization as a path to MLS

By Diana L. Hecht, PhD, and Warren A. Rosen, PhD, Rydal Research and Development, Inc.

#### Sky's the limit with satellite processors

40 Next-generation embedded processors empower satellite telemetry and command systems

By Dave Stevenson, Aeroflex Colorado Springs

#### **E-LETTER**

www.mil-embedded.com/eletter

Combating obsolescence in high-performance multiprocessor software

By William Lundgren, Kerry Barnes, and James Steed, Gedae

Modern battery technology distinguishes military handhelds – and presents significant design challenges

By Robin Sarah Tichy, PhD, Micro Power Electronics

Agile software development of military embedded systems

By Dominic Tavassoli, Telelogic

New surface mount power components drive military power supply modules

By Tracy Autry, Microsemi Corporation

### **E-cast**

**IMS and IP Network**

**Software-Defined Radio:** What you need to know Aug. 21, 2 p.m. EDT

#### **WEB RESOURCES**

Subscribe to the magazine or E-letter: www.opensystems-publishing.com/subscriptions

#### Live industry news:

www.opensystems-publishing.com/news/submit

**OpenSystems**

Publishing"

#### Submit new products:

www.opensystems-publishing.com/vendors/

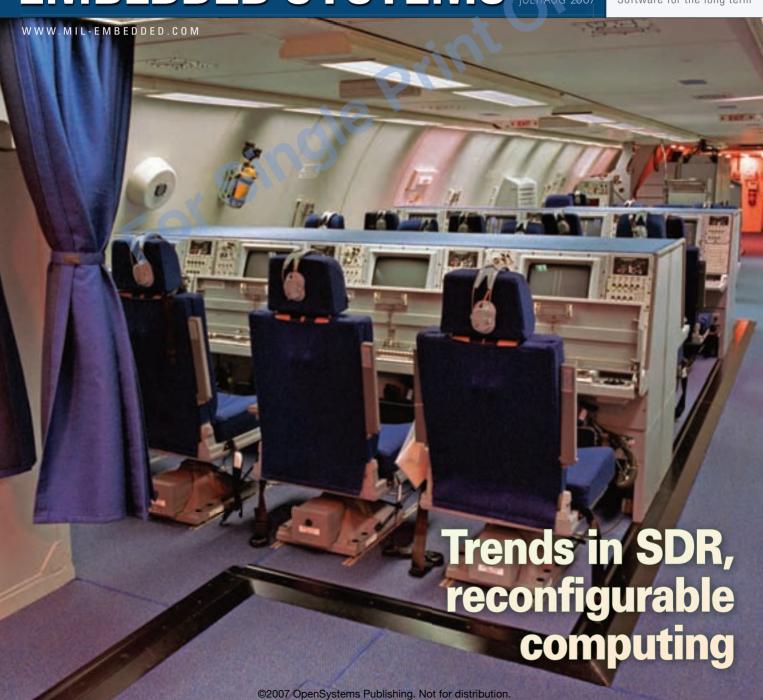

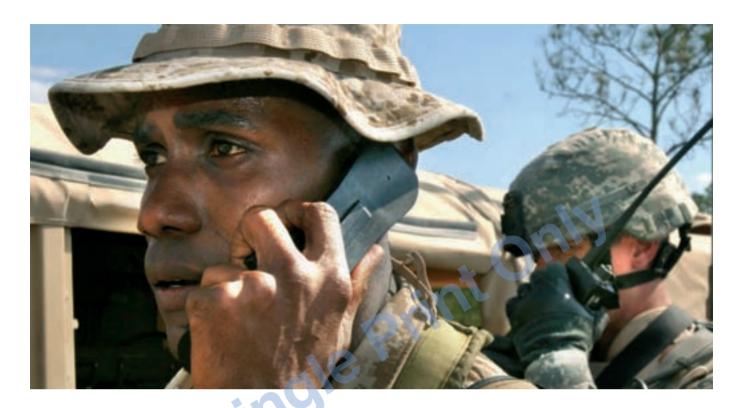

Boeing's latest 767 wide-body AWACS has ample room for operator consoles for air traffic control, blue force tracking, radar, and radios. Trouble is, a lack of radio interoperability means operators deal with one of each kind of radio or comm link – often receiving on one radio and verbally rebroadcasting on another. Software-Defined Radios are destined to solve this problem – and reduce the amount of radio gear and console space. See SDR articles starting on page 12. (Photo courtesy of Boeing)

demarks within *Military Embedded Systems* their respective owners. sning © 2007 Military Embedded Systems © 2007 OpenS

Published by:

4 / JULY/AUGUST 2007 MILITARY EMBEDDED SYSTEMS

#### **OpenSystems Publishing**

#### Advertising/Business Office

30233 Jefferson Avenue St. Clair Shores, MI 48082 Tel: 586-415-6500 Fax: 586-415-4882

Vice President Marketing & Sales Patrick Honner

phopper@opensystems-publishing.com

#### **Business Manager** Karen Layman

#### **Sales Group**

Dennis Doyle, Senior Account Manager ddoyle@opensystems-publishing.com

Tom Varcie, Senior Account Manager tvarcie@opensystems-publishing.com

Doug Cordier, Account Manager dcordier@opensystems-publishing.com

Andrea Stabile, Advertising/Marketing Coordinator astabile@opensystems-publishing.com

Christine Long, E-marketing Manager clong@opensystems-publishing.com

#### Regional Sales Managers

Phil Arndt – New England parndt@opensystems-publishing.com

Richard Ayer - West Coast rayer@opensystems-publishing.com

Barbara Quinlan - Midwest/Southwest

bquinlan@opensystems-publishing.com

Ron Taylor - East Coast/Mid Atlantic rtaylor@opensystems-publishing.com

#### International Sales

Account Manager - Israel daronovic@opensystems-publishing.com

#### **Reprints and PDFs**

Becky Mullaney - 717-399-1900, Ext. 166 mesreprints@opensystems-publishing.com

#### Advertiser Information

#### Page #/Advertiser

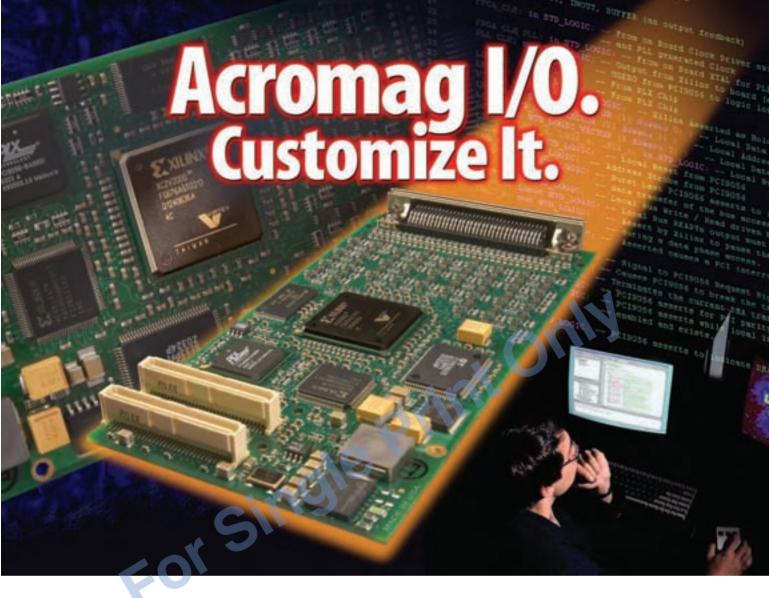

- 11 Acromag FPGA I/O

- 38 ACT/Technico Single Board Computers

- 45 AdvancedTCA Seminar AdvancedTCA Summit

- 31 Advantech Rugged Solutions

- 10 Aerofley Embedded Solutions

- 35 Annapolis Micro Systems FPGA Systems

- Az-Com Boards and Extenders

- 48 Curtiss-Wright VPX and CompactPCI SBCs

- 19 Data Device Corp. MIL-STD-1553

- DIGITAL-LOGIC In-Vehicle PCs 23

- Excalibur Systems MIL-SPEC Solutions

- GE Fanuc Embedded Systems Embedded Systems

- 5 Intel Embedded Solutions

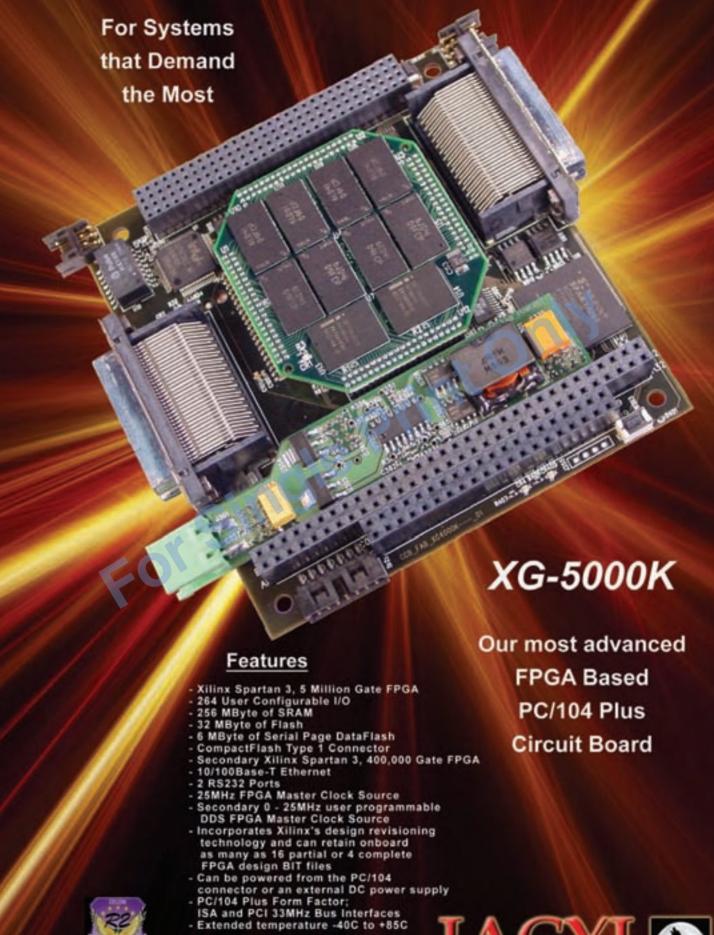

- 13 Jacyl Technology XG-5000K

- 27 Microbus Floard

- 6 Phoenix International Data Storage Modules

- PQI Europe Storage Solutions

- 24 RTD Embedded Technologies PC/104 Modules

- 3 Synplicity DSP Design

- Targa Systems Division Network Attached Storage

- 21 Technobox PMC Solutions

- 8 TEWS Technologies I/O Solutions

- 34 Tilcon Software Ltd. – Embedded Solutions

- 37 Tri-M Systems Embedded Products

- 39 Tri-M Systems Embedded Products

# MISSION CRITICAL VME/CPCI

Extreme Comprehensiveness: We offer the most comprehensive. VME/cPCI storage product line in the world, offering device alternatives for any standard or unique application.

· Solid State Disk · Removable Hard Disk • Tape Drives • Optical Disk • PCMCIA Adapter

Extreme Performance: Our VME products feature extreme speed, capacity and ruggedly reliability with 320 MB/sec throughput enabled by LVD SCSI technology, storage capacity of more than 600 GBs per module and a 1,400,000 hour MTBF.

Extreme Quality: Phoenix International is the only manufacturer of VME data storage products. that is ISO 9001:2000 Certified.

Phoenix International Systems, Inc. An ISO 9001:2000 Certified SDV0S8

714-283-4800 • 800-203-4800 • www.phenxint.com

#### OPENSYSTEMS PUBLICATI

#### Military and Aerospace Group

- DSP&FPGA Product Resource Guide

- DSP-FPGA.com

- DSP-FPGA.com E-letter

- Military Embedded Systems

- Military Embedded Systems E-letter

- Military Embedded Systems Resource Guide

- PC/104 & Small Form Factors

- PC/104 & Small Form Factors E-letter

- PC/104 & Small Form Factors Resource Guide

- VME and Critical Systems

- VME and Critical Systems E-letter

- VME and Critical Systems Resource Guide

Group Editorial Director Chris A. Ciufo

cciufo@opensystems-publishing.com

Senior Editor (columns) Terri Thorson

tthorson@opensystems-publishing.com

**Assistant Editor** Sharon Schnakenburg

sschnakenburg@opensystems-publishing.com

Copy Editor Robin DiPerna **European Representative** Hermann Strass

hstrass@opensystems-publishing.com

Art Director Steph Sweet

Senior Web Developer Konrad Witte **Graphic Specialist David Diomede**

> Phyllis Thompson subscriptions@opensystems-publishing.com

# OpenSystems Publishing

Editorial/Production office:

Circulation/Office Manager

16872 E. Ave of the Fountains. Ste 203. Fountain Hills. AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystems-publishing.com

Publishers John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

#### **Communications Group**

**Editorial Director** Joe Pavlat **Assistant Managing Editor** Anne Fisher Senior Editor (columns) Terri Thorson Technology Editor Curt Schwaderer **European Representative** Hermann Strass

#### **Embedded and Test & Analysis Group**

**Editorial Director** Jerry Gipper **Editorial Director** Don Dingee Jennifer Hesse Associate Editor **Technical Editor** Chad Lumsden Special Projects Editor **Bob Stasonis** European Representative Hermann Strass

ISSN: Print 1557-3222

Military Embedded Systems (USPS 019-288) is published six times a year (January/ February, March/April, May/June, July/August, September/October, November/ December) by OpenSystems Publishing LLC, 30233 Jefferson Avenue, St. Clair Shores, MI 48082.

**Subscriptions** are free to persons interested in the design or promotion of *Military Embedded Systems*. For others inside the US and Canada, subscriptions are \$28/year. For 1st class delivery outside the US and Canada, subscriptions are \$50/ year (advance payment in US funds required).

Canada: Publication agreement number 40048627

Return address WDS, Station A PO Box 54, Windsor, ON N9A 615

POSTMASTER: Send address changes to Military Embedded Systems 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

# **Industry Analysis**

# SWEPT up for real?

By Don Dingee

I had no idea that we would be Slashdotted when we posted the Raytheon news release entitled *Raytheon Develops World's First Polymorphic Computer* on our Mil-Embedded.com RSS newsfeed March 20. I thought I would try to go deeper behind the scenes for the back story on this.

In 1999, Robert Graybill began his term as program manager at DARPA, laying out a vision for embedded computing. "As we look at future systems, they are anything but bounded and will need to evolve with each mission and with technology advances. Translated into computer architecture terms, this means the architecture must be able to support a broad spectrum of functionality by morphing on demand over time. At the same time, each unique mission's functionality, size, weight, energy, performance, and time requirements must still be satisfied, and hence the term *polymorphous computing*."

I like the SWEPT acronym Graybill proposed better than what we usually call *SWaP* (Size, Weight, and Power), as *power* can be a bit ambiguous.

In May 2005, Raytheon was awarded the contract for the Morphable Networked Micro-Architecture (MONARCH) project, working with the Information Sciences Institute (ISI) at the University of Southern California, with assistance from IBM, the Georgia Institute of Technology, and Mercury Computer Systems.

On March 20, we received the news of the first breathing prototypes of a MONARCH chip delivered from the IBM fab to Raytheon. MONARCH combines six RISC cores coupled into a Field Programmable Computing Array (FPCA), with a morphing interconnect to optimize memory access and routing between clusters, and two RapidIO ports for connecting industry-standard devices.

Jeff LaCoss, ISI principal architect, says: "The RISC engines are only a part of the MONARCH chip. Stream processing (such as FFTs) are handled by Raytheon's Field Programmable Computing Array (FPCA). The RISC ISA is an ISI invention developed for the DIVA Architecture, an earlier DARPA-funded project at ISI. The ISA is modeled on the MIPS R3000 ISA, and is also much like the Hennessey and Patterson DLX ISA."

The RISC engines and the stream processing FPCA can work closely together. According to LaCoss, the RISC processors have two modes of operation: "They can run in 32-bit mode like an R3000 with floating point. However, the chip can *morph* and assign resources from the stream processor to the RISC engines. These resources become a 256-bit WideWord data path that behaves similarly to a SIMD processor executing in place of the RISC 32-bit data path. That is, the RISC engine runs instructions for either 32- or 256-bit mode."

This gives MONARCH the horsepower for complex algorithms, and LaCoss gives an example. "A killer app for the WideWord is the corner-turn algorithm, something that conventional CPUs are terrible at. The WideWord can turn an 8 x 8 array of 32-bit objects in around 150 clock cycles, 8 memory reads, some permutations, and 8 memory writes. A conventional processor (such as an R3000 or Power Architecture) must do 64 reads to get the data, 64 writes to store the data, plus a whole bunch of addressing calculations. That's a lot of clocks and instructions. Caches help conventional processors (MONARCH has none) but don't cure the memory-access latency problems."

The RISC engines run an RTEMS-derivative RTOS written by Exogi under subcontract to ISI. Software tools include a production-quality C++ 4.1 compiler written for ISI by CodeSourcery. The assembler is an ISI tool based on GNU *gas*. There are cycle-accurate simulators for the RISC engines, the FPCA stream-processing fabric, and the chip as a whole.

Boutique processors developed for specific jobs should help optimize SWEPT – Size, Weight, Energy, Performance, and Time – to new levels.

### Field Intelligence

# Inside Ethernet switch source code

Many military platforms are adopting GbE as their backbone intraplatform network. The U.S. Navy has been using Ethernet for many years in combat systems, but many other types of platforms are also turning to Ethernet for its ease and economy of implementation, its wealth of hardware support, and its performance. Some of these new adopters are satisfying requirements for the Global Information Grids (GIGs) IPv6 mandate, but many are adopting Ethernet purely on its merits. Ethernet switches are essential elements of a network and are readily available in stand-alone or embeddable formats, covering the complete spectrum of environmental requirements from the benign office to the harshest military specifications.

The choice of network or switched fabric for a particular application is complex, and more than one type may be employed on a platform to achieve optimum performance. The characteristics of the primary contenders can be summarized:

Serial RapidIO - High performance, high data integrity, low-latency switched fabric for interconnection of many

COTS I/O Solutions for:

IndustryPack®, PMC, CompactPCI, PCI

with Outstanding Software Support.

CPU Carriers

IP and PMC Carriers

Ethernet

Communication

CAN Bus

Field Bus

Digital I/O

Anabog I/O

PC Card/CardBus

Motion Control

Memory

User-programmable FPGA

TEVNS

COS-9

TEVNS

TECHNOLOGIES LLC: FIND Distin Dissured Parkets, Buts 127-Rose My MRZ 1455A

Plant 1 (TR) EDSC-fox 1 (TR) 2015 EBT 1 Emma 1021-Rose My MRZ 1455A

Plant 1 (TR) EDSC-fox 1 (TR) 2015 EBT 1 Emma 1021-Rose My MRZ 1455A

Plant 1 (TR) EDSC-fox 1 (TR) 2015 EBT 1 Emma 1021-Rose My MRZ 1455A

Plant 1 (TR) ETCHNOLOGIES Geden, An Barletof 1 (Treat and anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

TEVNS TECHNOLOGIES Geden, An Barletof 1 (Treat anabolications are

- ports within a chassis. Typically Serial RapidIO is used in multicomputing environments for DSP applications.

- Fibre Channel Supports concurrent protocols such as SCSI and IP on the same network. It has flexible topologies and for small systems can be configured without a switch. The use of fibre at the physical level offers inherent protection from electromagnetic effects, making it suitable for military applications. The primary commercial use of Fibre Channel is in Storage Area Networks (SANs).

- » PCI Express High-performance, scalable, serial connection using PCI-like memory mapping; often used for connection to high-speed peripheral devices or sensors; similar to PCI as it has a single master that controls access.

- >> Ethernet High-performance network with 1 Gbps readily available now, 10 Gbps being introduced; synonymous with the Internet and IP. It can be used as an interconnect at many levels from board to board, between chassis, between systems, as an intraplatform private network and, of course, extending to the Internet or the military's GIG.

Key to the performance and interoperability of switches is the onboard software, including protocol, management, and operating system. The functions of a switch are controlled by IEEE standards for the physical and signaling levels and by Request for Comments (RFCs) published by the Internet Engineering Task Force (IETF) for the switching, routing, and management of the switch. Vendors of switches often make use of off-the-shelf, real-time operating systems and commercially produced protocol software to provide a complete packaged product for their customers. However this is not always the ideal solution for long-running military programs where the customer may want to "freeze" at a particular revision of software and still receive support, or have the ability to pass on limited rights to the source code to their end customer.

When Ethernet is used in real-time intraplatform networks, there can be timing and response parameters that can be modified for performance or determinism just for that platform, requiring easy access to the source code for modification and its subsequent long-term support. An example of this is the Spanning Tree Protocol (STP), which is used to determine the optimum routing of messages through a network. When any new connection is made, it must first listen and learn the applicable routing of the network before establishing its normal operation. A root bridge (switch) is elected, and the STP then creates paths through the network from switch to switch, using the shortest routes in a tree structure. Without STP, this routing might create loops resulting in broadcast storms from switch to switch. STP can take a matter of minutes to establish new routing before a device can become active on the network. To address this delay, Rapid Spanning Tree Protocol (RSTP) was introduced to provide a more rapid convergence of the tree, but there are specific cases in critical networks where yet faster reconvergence is needed.

An intraplatform network, such as might be implemented on an armored fighting vehicle, an Unmanned Aerial Vehicle (UAV), or a naval vessel's combat system, is essentially a closed private network. The network will have been designed with many redundant paths to provide enhanced survivability in the event of battle damage. Waiting many seconds for the RSTP to reestablish network routing if active paths are lost would be unacceptable, but within the closed network environment, it is possible to change the parameters of the RSTP outside its normal limits to provide much faster response to path failures. By reducing the time to detect failures and reestablish network routing, an intraplatform network can be tailored to suit the criticality requirements of a specific platform yet still retain the economy and ease of use that Ethernet offers.

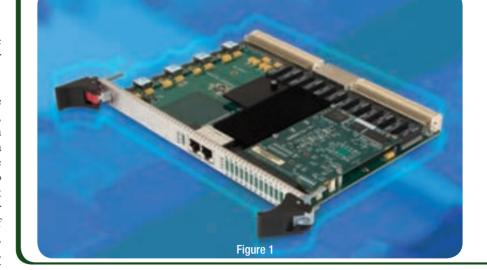

Access to switch source code and the ability to make rapid changes to suit particular customer requirements are both essential ingredients of success in tailoring commercial technologies to suit the sometimes unique requirements of military programs. Recognizing this, GE Fanuc has introduced OpenWare, a switch management package configured from a mix of modules written in-house and from open source to provide the complete protocol, management, and operating system suite for their new range of NETernity Ethernet switches supporting both IPv4 and IPv6. The RM922C, a 24-port switch in 6U VME format, is shown in Figure 1.

Leveraging the best that the commercial technology base has to offer has many advantages for military programs. It translates into lower development costs, faster time-to-deployment, and less risk. However, there are times when the best needs to be better in order to meet the most stringent military requirements. Ethernet switches use tried and tested technology that can be improved on where safety, time-sensitivity, and fail-safe operation are more critical than their commercial counterparts. But this requires the access and capability to modify a switch's source code. Providing this will only serve to enhance Ethernet's adoption into a broader range of critical and strategic military platforms, many of which continue to use proprietary solutions today.

To learn more, e-mail Duncan at young.duncan1@btinternet.com.

# **Guest opinion**

# Developing defense software systems for the long term

By Gary Cato

Military software built with obscure or unproductive programming languages has proven to be an expensive problem. The exploding complexity of software systems creates an imperative for techniques that not only focus on development productivity but will have the commercial popularity and longevity to avoid costly obsolescence that threatens military systems today. Military programs should increasingly look toward Java-based solutions both as a means to drive up productivity and to stave off obsolescence.

Mission-critical software's complexity continues to increase, keeping pace with hardware capacity expansion. Increasing software complexity is a fact of life that begs for technology solutions to manage it. Ironically, as software complexity has increased, so has the use of C++ (and C) in mission-critical development. C++ does not scale well as system complexity grows. There are a number of reasons for this, some within the language itself and others within the ecosystem surrounding the language.

Since the elimination of the Ada mandate nearly 10 years ago, a great deal of pressure within the DoD has resulted in more and more new programs using C++ in a belated chase for access to a more commercially successful language. The result has been a dangerous dumbing down of development for mission-critical software even as complexity has continued to increase.

The commercial success and technical superiority of Java provide a better path. The failures in modularity and scalability of C++, and its inherent high error rates and lack of safety, are absent with Java. While Java enjoys modularity, safety, and scalability similar to Ada, Java also enjoys commercial appeal and support surpassing even C++. Java is now used more broadly on desktop and enterprise applications than C++ and is finding increasing acceptance in embedded and mission-critical applications, thanks to a new generation of technologies friendly to the rigorous needs of resource-constrained systems: native compilation, predictable threading, real-time memory management, and high-efficiency standard libraries.

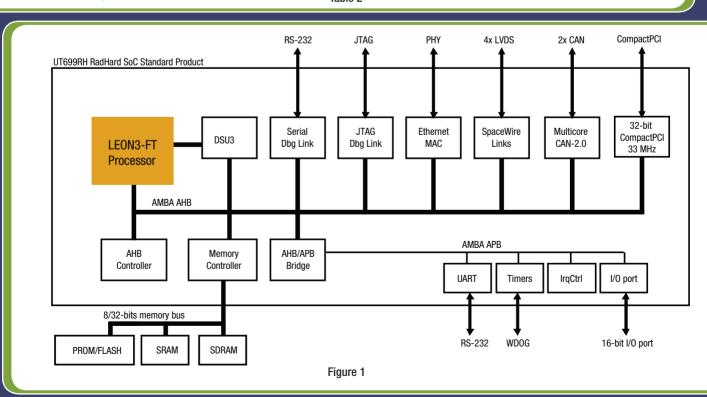

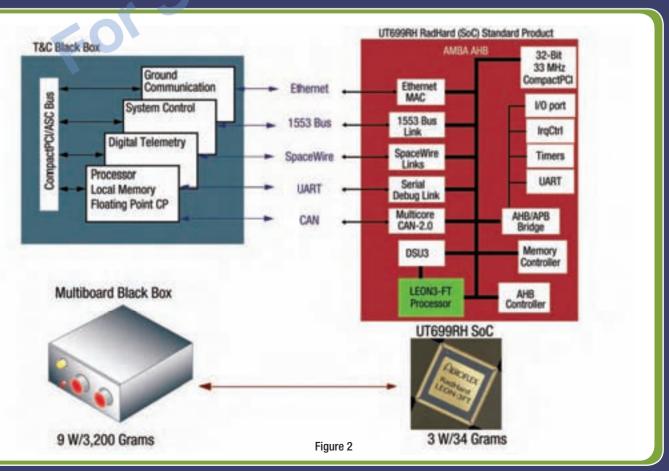

# Space system engineering from development to flight

#### **Aeroflex Colorado Springs**

invites you to discuss your space programs with us. We can assist you in technology selection, proof of concept, and flight solutions. New technology additions to the Aeroflex RadHard portfolio include the LEON 3FT µProcessor and a 16-port SpaceWire Router. Plan your next generation system today with Aeroflex QML Q&V RadHard components. We can do it for you.

800-645-8862

www.aeroflex.com/ME707

Java technology has been shown to result in a 2-3x improvement in programming productivity compared to C++, an increasingly vital factor in managing the escalating costs of mission-critical software development. Java also has been shown to result in up to 80 percent fewer errors than C++, containing the costs of integration and long-term maintenance in the face of growing software complexity.

Ada remains a great language. However, when the decision is made for a new program to follow a path other than Ada, C++ is a poor substitute that will be a persistent source of errors and high lifetime cost. Java is a vastly superior alternative to C++ that must be given serious consideration for all new mission-critical programs.

Gary Cato, director of strategic alliances at Aonix, can be reached at: gary.cato@aonix.com.

## Acromag introduces affordable FPGA I/O. For ALL your projects.

s an engineer, your projects are unique, ever-changing, and budget-bound. That's why our new PMC modules give you an affordable solution to create custom I/O boards.

But if you thought FPGA computing was only for top-end applications, think again. Our PMCs are ideal for protocol conversion, simulation, in-circuit-testing, and much more.

So, why settle for generic I/O when you can design exactly what you need while staying in budget and reducing your time to market?

- Virtex®-II, Virtex-4, Acex®, and Cyclone®-II FPGAs

- Large DRAM buffers and dual-ported SRAM

- Conduction-cooled models available

#### Cost-effective custom I/O

Choose from a variety of I/O configurations:

- Digital I/O: TTL, CMOS, RS422, or LVDS I/O

- Analog I/O: 16-bit 100MHz A/D, 900KHz D/A

#### **Faster time to market**

Why waste precious time building a board from scratch? Our new FPGA modules let you process your I/O signals any way you want. Quickly.

#### Flexibility to meet unexpected challenges

Acromag FPGA I/O will help you bring your projects in on time and under budget. And with

FPGAs, you'll be ready to adapt to all the inevitable changes.

Thinking about FPGA I/O?

Think flexible. Think affordable.

Think Acromag.

www.acromagembedded.com 877-295-7088 or 248-295-0310

DIGITAL I/O

FPGA

COUNTER/TIMER

QUADRATURE

SERIAL I/O

# Trends in SDR and reconfigurable computing

# Next-generation SDR operating environment takes on SWaP challenges in resource-constrained platforms

By Dominick Paniscotti and Jerry Bickle

Traditional Operating Environments (OEs) are struggling today to meet the high data rate performance and stringent Size, Weight, and Power (SWaP) requirements of resource-constrained SDRs. To address these challenges, a next-generation COTS, standards-compliant SDR OE is needed – one that is supported by a finely tuned middleware, vertically integrated, and performance optimized.

First-generation standards-based SDR OEs – originally defined by Department of Defense (DoD) contractors on the Joint Tactical Radio System (JTRS) program (see sidebar) – have reached their performance ceiling. A new breed of OE is necessary to ensure that the benefits of SDR and the JTRS program are fully realized.

When the JTRS program kicked off several years ago, OEs were developed by building custom implementations of SCA-compliant Core Frameworks (CFs) on top of existing COTS middleware products. Given the multivendor nature of these initial JTRS

OE implementations, potential for end-to-end performance optimizations was limited. Further, specialized processors such as DSPs and FPGAs, commonly used in resource-constrained platforms, interfaced with these OEs through a high-overhead custom Hardware Abstraction Layer (HAL). The result: First-generation SDR OEs have been handcuffed performance-wise and struggle to meet increasingly high data rates and stringent SWaP requirements for resourceconstrained, small form factor SDRs.

To pick up where original OEs have maxed out, next-generation COTS, standards-compliant SDR OEs need to

be developed as vertically integrated, performance-optimized products. These new OEs must feature small memory footprints and have the ability to run on any mix of General Purpose Processor (GPP), DSP, and FPGA processor technologies. They also need to be supported by a finely tuned COTS and standards-based middleware and optimized for performance across the complete runtime SDR architecture. It is this mix of qualities that will ensure that SDR is viable across a wide range of resource-constrained platforms.

#### Middleware is a critical component

Middleware's role in next-generation OEs cannot be overstated. Middleware is "where the rubber meets the road" for SDR. At its very essence, middleware provides location-transparent communications between waveform components and enables these components to be located on different processors in an SDR. To achieve this task, it is crucial that it operates efficiently with both the underlying operating system and the CF.

#### **JTRS OE**

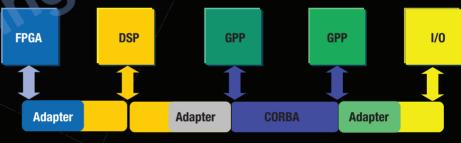

A standards-based SDR OE was defined by DoD contractors on the Joint Tactical Radio System (JTRS) program to address radio waveform interoperability requirements. This OE, specified by the JTRS Software Communications Architecture (SCA), comprises a Core Framework (CF), CORBA middleware, and an Operating System (OS) with associated board support packages, as illustrated.

The OE imposes design constraints on waveforms and other applications to provide increased portability of those applications from one radio platform to another. These design constraints include specified interfaces between the core framework and application software, as well as restrictions on operating system waveform usage. The SCA thus provides a development rule set focused on the detailed radio set, waveform and software development standards, and specifications that describe how to make the system designed to it interoperable. The core framework is an architectural concept defining the essential "core" set of open software interfaces and profiles that provide for the deployment, management, interconnection, and intercommunication of software application components in embedded, distributed-computing communication systems.

| WF Component Implementation |                           |                             |  |  |  |  |  |  |  |

|-----------------------------|---------------------------|-----------------------------|--|--|--|--|--|--|--|

| Core/Component<br>Framework | Executable Device         | WF Component Infrastructure |  |  |  |  |  |  |  |

|                             | Communications Middleware |                             |  |  |  |  |  |  |  |

|                             | Operating System          |                             |  |  |  |  |  |  |  |

Advancing Today's Technology into Tomorrow www.jacyltechnology.com However, when building their first-generation SDR OEs, radio manufacturers undertook the significant effort of building custom core frameworks and integrating them with operating systems and existing COTS CORBA middleware – as specified by the Software Communications Architecture[1][2] (SCA). Therefore, optimization potential of this multivendor, integrated solution was inherently limited, and has resulted in large memory footprints and suboptimal performance.

Compounding this middleware challenge is the fact that CORBA historically has been associated with large enterprise applications, not real-time embedded systems. It is only now that next-generation OEs can benefit from the significant effort that has been devoted in recent years within the middleware community to streamline CORBA for use in embedded, real-time applications.

For example, new OMG CORBA standards such as CORBA/e[3] have been introduced to address the most demanding requirements of performance-based embedded applications without forfeiting interoperability, portability, and platform independence. Designed to dramatically reduce the footprint and overhead of typical enterprise middleware, this new standard eliminates much of the dynamic and resource-consuming aspects of CORBA, thereby facilitating implementations that can meet the stringent requirements of real-time embedded systems such as SDRs.

the specialized interfaces, and decreased performance (latency and throughput) due to the processing overhead of these adapters. These HALs were proprietary in nature and not based upon open standards. Also, waveform developers were forced to implement custom message protocol handlers in addition to the waveform logic required to deliver radios to their customers. This handcrafting of message protocol handlers ultimately led to increases in development and maintenance costs.

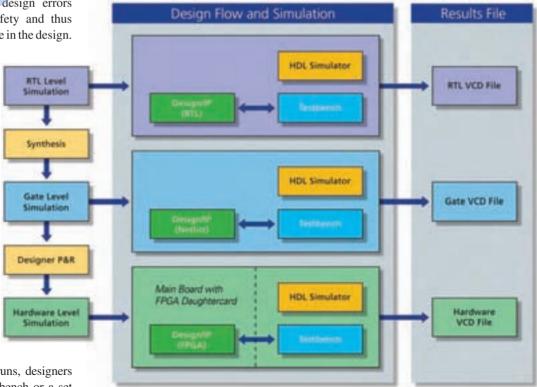

Today, next-generation OEs employ an alternative approach, in which the use of standards-based, COTS communications middleware is extended across all processor types, as shown in Figure 2, bringing architectural consistency throughout the SDR.

For SCA-compliant SDRs, this architectural consistency had been achieved by utilizing the high-performance, small footprint CORBA ORBs available DSPs, FPGAs, and GPPs. Now, waveform components implemented on each of these processors may communicate with others without knowledge of their location and without handcrafting special protocols or adapters. This ubiquitous standard communication layer allows radio developers to retarget their software to lower-cost, higher-performance, lower-power platforms as processor technologies continue to mature.

#### The processor challenge

To meet the stringent SWaP requirements of resource-constrained platforms, specialized processors such as DSPs and FGPAs are often used in the design of an SDR. Therefore, the logical SDR architecture described earlier should map to a physical architecture consisting of these specialized processors as well as GPPs, with waveform components executing on and communicating across all three processor types.

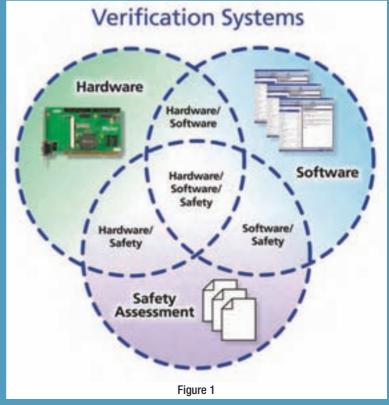

As mentioned earlier, first-generation OE designers implemented adapters, or HAL, to enable waveform components implemented on these specialized processors to communicate with components implemented on GPPs, as shown in Figure 1. These adapters required the implementation of custom message protocols, which resulted in decreased waveform component portability due to

Figure 1

Figure 2

### The ISV community and next-generation OEs

There has been much promising work within the Independent Software Vendor (ISV) community on developing next-generation OEs. ISVs are developing OE solutions that can maintain the full functionality of first-generation OEs, yet are not dependent on underlying operating systems or compilers to achieve small memory footprints. And maybe most appealing to system integrators and SDR developers, these next-generation platform-independent OEs provide a direct plug-and-play OE replacement for existing SDRs needing to reduce SWaP. They also provide SDR developers with a flexible, cost-effective COTS alternative to internally developed solutions.

To address DSP resource constraints, next-generation OEs leverage the availability of high-performance, COTS middleware specifically designed and optimized for DSPs. For example, PrismTech delivers a C language CORBA ORB utilizing 75 percent less memory than comparable C++ implementations. A reduction in memory footprint, when achieved without any sacrifices in performance or functionality, enables the deployment of SDR architectures on DSPs and allows a common SDR architecture to be used seamlessly across the increasingly typical processor types used in SDRs.

For FPGA-based components, hardware ORBs are used in second-generation OEs to enable CORBA-based communication between FPGAs, DSPs, and GPPs. Implemented as portable VHDL cores, these types of hardware ORBs can be used by radio developers with FPGAs or as part of an ASIC.

This is in contrast to first-generation SDR implementations that attempted to extend CORBA to FPGAs by executing a CORBA ORB on embedded processor cores within an FPGA. This approach not only failed to achieve the desired portability, consistent SDR architecture, and SDR SWaP goals, but it also decreased throughput and increased latency because adapters were still required within the FPGA.

Because of the architectural consistency of next-generation OEs, new radio platform configurations are available to address the stringent SWaP demands of resource-constrained systems. It is now feasible to implement an SDR-compliant, handheld radio using only DSPs, or just DSPs and FPGAs. Recent proposals from the DoD also request SDR platforms with precisely these processor configurations.

Another key technology utilized in next-generation OEs is the CORBA Extensible Transport Framework (ETF). This framework allows the development of standard and efficient protocols to support optimized communication between ORBs. Off-theshelf ORBs typically provide TCP/IP transports that are not adequate for many real-time, embedded, constrained systems. ETF provides the mechanisms for adding other efficient, high-performance transports to take advantage of high-speed serial or parallel interfaces such as RapidIO and CompactPCI.

#### **Next-generation OEs are available today**

In summary, next-generation SDR OEs address SWaP concerns without constraining processor hardware choices while providing the benefits of a consistent SDR architecture.

Small footprint, high-performance OEs with static memory footprints of well under 1 MB are available today. This 3-10x reduction in size makes standards-based SDRs viable for even the smallest form factor applications. In addition, companies such as PrismTech are also offering the Integrated Circuit ORB (ICO) for FPGA and ASIC SDR platforms to provide end-to-end architectural consistency across all processor types in use today for SDR platforms.

#### The new OMG software radio specification

Additional SWaP savings can be realized by SDR OEs based upon the new OMG software radio specification[4] and the flexibility inherent in this standard. The standard, which represents the SCA's commercial evolution, allows SDR developers to tailor their solutions by eliminating architectural features, as needed, to deliver only the SDR features required by their end users.

The availability of these next-generation OEs relieves radio manufacturers of the development and maintenance burden associated with custom OEs and significantly accelerates time to market for their SDR products. As a result, application developers using these architectures can now focus on delivering radio functionality rather than struggling to build proprietary middleware to allow communication between the disparate processors used within SDRs. The technological advances in next-generation OEs along with the commercial availability of optimized implementations for the military and commercial markets has made SDR an available reality today.

#### References

- Software Communications Architecture 2.2, http://jtrs.spawar.navy. mil/sca/downloads.asp

- Software Communications Architecture 2.2.2, http://jtrs.spawar.navy. mil/sca/downloads.asp

- CORBA/e and RT CORBA, www.omg.org/technology/documents/ specialized\_corba.htm

- OMG PIM and PSM for Software Radio Components, www.omg.org/ technology/documents/profile\_catalog.htm#UML\_for\_SWRadio

Dominick Paniscotti, PrismTech's VP Engineering, SDR Products, has been involved in SDR design and development since 1998. He is a cofounder of the Object Management Group (OMG) software-based communication task force and actively

supports the commercial standardization of SDR technologies via the SDR Forum. He earned his BSEE from Fairleigh Dickinson University.

Jerry Bickle, PrismTech's Chief Scientist, SDR Products, has been involved in SDR development and design since 1997. He and Dominick Paniscotti coauthored the JTRS Software SCA 2.2 specification, and Jerry has also served as a

member of the JTRS Technical Architecture Group (TAG). He helped lead the SDR Forum's SCA adoption and the formation of the OMG software-based communication task force. He holds a BA in Computer Science and Mathematics and an MS in Secondary Education from Northern Illinois University.

#### **PrismTech Corporation**

6 Lincoln Knoll Lane, Suite 100

Burlington, MA 01803

781-270-1177

info@prismtech.com

www.prismtech.com

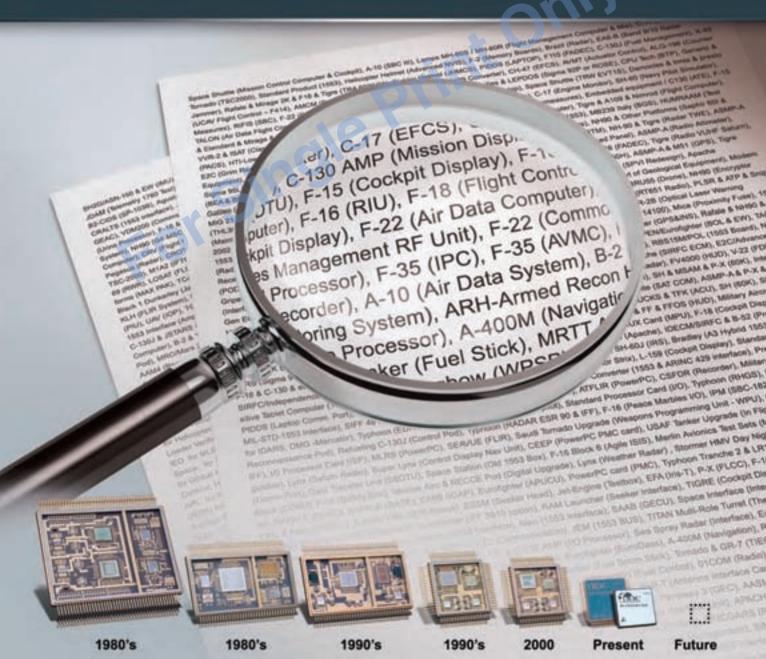

Technology insertion using COTS FPGA-based products promises to deliver significant benefits but requires adequate planning up front. Success involves both hardware and software strategies. Following a common hardware model and minimizing connector pin changes are key to easing hardware technology insertion issues. Software problems can be mitigated through the use of highly abstracted APIs from one product generation to the next.

Over the past decade, the concept of "technology insertion" has become a sort of mantra for the Aerospace and Defense (A&D) community, promising an approach for upgrading fielded systems with the latest, most advanced technology with the least delay. The rapid pace of technological innovation – and subsequent obsolescence - has made technology insertion critical for the success of multiyear A&D development, test, and deployment projects. Unmanned Aerial Vehicles (UAVs), radar, and SIGnals INTelligence (SIGINT) are examples of sophisticated platforms that have benefited from technology insertion. To fully understand the challenges of technology insertion, including complexity and cost, it's useful to consider what is involved in successfully using this approach for upgrading legacy systems. Using FPGAs in a reconfigurable computing application provides a good example of the benefits and challenges entailed in making technology insertion work. This example also enables examination of some common issues associated with technology insertion in such applications, how COTS vendors can best help their customers to address those problems, and how the overall technology insertion problem can be significantly eased by proper planning.

#### Using FPGAs in technology insertion

The basic problem domains involved in technology insertion can be roughly categorized as:

- >> Hardware How the equipment physically connects

- System software How the operating environment, system libraries and utilities, drivers, and middleware provide an infrastructure for applications

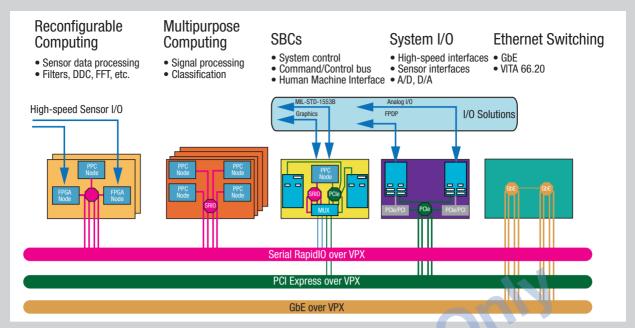

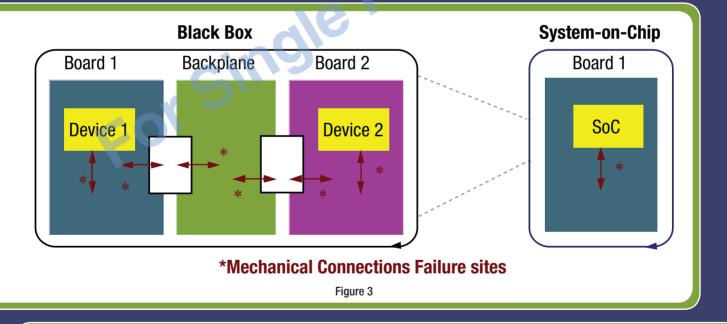

Using FPGA technology in an embedded multicomputing system provides an interesting case example because it straddles both the hardware and system software domains. FPGAs fall into the hardware domain because they are physically integrated to hardware elements, and the developer must work very closely with these elements when designing an application. However, FPGAs present a software challenge as well since they must be programmed and often incorporate vendor or third-party supplied "blocks" or "IP." In addition, a general purpose processor using system library calls is typically used to configure the FPGAs and the commands they use to communicate with other processors and devices in the system. Such systems are often complex and heterogeneous as shown in Figure 1.

For technology insertion, the ideal scenario is a plug replacement module that requires no hardware or software changes. While historically uncommon for FPGA-based computing products, this scenario can also often be undesirable since state-of-the-art computing platforms can offer new, more advanced features that system integrators can use to their advantage. The goal for the system integrator must therefore be to maximize the benefits of technology insertion while minimizing the impact on the existing system. The degree of flexibility in the hardware and software domains can be directly affected by early design choices made by the system integrator and the products offered by COTS vendors.

The simplest approach for a COTS vendor to ease technology insertion hardware problems is to follow a common hardware model from generation to generation of platform and to minimize connector pin changes. Industry board and module standards such as VME, VPX-REDI (VITA 46/48), PMC (VITA 32), and XMC (VITA 42) address a large part of this problem by specifying fixed form factors and pin definitions for board I/O such as buses or switched fabric interconnects. Vendors can extend this model by maintaining pin footprints across product generations for such common interfaces as serial ports and Ethernet.

Figure 1

The same also holds true for FPGAs. A common, or at least similar, I/O footprint minimizes the need for radical redesign during a technology insertion project.

#### The importance of software

Although FPGA development is very tightly linked to the target component and platform hardware design, there is a lack of standardized or industry-accepted tools and frameworks to abstract this linkage. The result is that software can typically have an even greater effect on a technology insertion program than hardware. The software challenges can be somewhat mitigated on general purpose processors by using off-the-shelf operating systems such as VxWorks or Linux, supported with full-featured BSPs, communications middleware, and application frameworks. For COTS vendors of FPGA products, the challenge is to provide development tools to the integrator to ease technology insertion while maintaining the performance demanded by the application developer. A common approach is for the COTS vendor to develop a standard "wrapper" or gasket that essentially represents the static infrastructure, such as interfaces to A/Ds, memories, Ethernet, and so on. The blocks and infrastructure should be designed to support a set of commonly implemented use cases in the most efficient manner possible, so as to minimize the size of the wrapper. Ideally, such infrastructure would represent only 5 to 10 percent of the total die size of the FPGA.

#### **Software support of FPGAs**

No less important than the ease of integrating existing application code into a new FPGA platform for a technology insertion project is the integration of the FPGA-based application into a larger multicomputer system. General purpose computing elements are often closely tied to the system's FPGAs by performing various command and control functions such as DMA engine control. Subsequently, the ease of a technology insertion can be directly affected by how well a vendor can maintain APIs from one product generation to the next, which, in turn, is often linked to the level of abstraction in the API: The more abstraction, the less likely it is that the API will change between product generations. One of the key tasks of an external processor is the command and control of

data movement both within the FPGA and between the FPGA and other general purpose processing nodes.

#### Making technology insertion real

There are many examples of a common hardware strategy from several COTS vendors that aid technology insertion. One example can be seen in Curtiss-Wright's latest-generation VPX-based board products. The three primary computing platforms in this product line – a dual 8641-based SBC, a quad 8641-based DSP engine, and the dual Xilinx Virtex-5 (Figure 2) FPGA-based CHAMP-FX2 (Figure 3) board – all share a set of common hardware design elements and were

Figure 2

Figure 3

specifically designed with common pin footprints for common I/O elements. For instance, the FPGA board not only shares the PowerPC node design elements with the two other VPX boards, but it also closely resembles its preceding VME version in its I/O and memory configuration.

The design of the VPX FPGA board and its VME predecessor took a balanced approach between the twin goals of maximum technology insertion value and minimum insertion effort. Their Continuum FXtools design kit provides a highly optimized set of IP blocks focused on the peripheral I/O and memories, with only a lightweight, scalable switching block and a few additional utility blocks to ease application integration. By providing a minimal but highly optimized infrastructure, FXtools abstracts those common I/O and memory objects without sacrificing performance. Designing with these IP blocks and adopting basic use cases can help ease future technology insertion.

To ease both the integration and technology insertion of FPGA-based computing elements, the boards' Continuum IPC communications middleware was extended to directly control DMA-based data transfers involving the FPGA node. The IPC software enables the application developer to create named buffer and data transfer objects that are globally visible to the system. Thus, any processor in the IPC system can create named buffers, attach to already created named buffers, and create data transfer objects between buffers, without having to resort to code-manipulating complex memory map translations or DMA command packet creation.

#### Hints for avoiding technology insertion headaches

While hardware and system software commonality across product generations is an important element in planning a successful technology insertion project, the application developer and system integrator can themselves play an important role in defining how difficult a future technology insertion project may be. For example, if the application developer bypasses vendor or OS APIs to directly manipulate hardware, the resulting code will be significantly less portable to future hardware platforms. However, there are a number of other ways in which an application developer or system integrator can structure their application/ system to minimize technology insertion headaches.

The first rule of designing for later technology insertion should be: "Don't fight the system software or OS." Most software frameworks, such as a BSP, utility library, or communications middleware like Continuum IPC, are designed with one or more basic use cases or design patterns in mind. One of the easiest ways for a developer to introduce problems in a later technology insertion project is to bend the software framework to match their favorite design pattern. Doing so virtually ensures that a later developer will have to bend things in a different way simply to make it work. The same holds true for the FPGA IP developer. While implementation details and interfaces may shift from one product generation to the next, the basic design patterns usually do not. Using vendor-supplied IP blocks and data flows in the manner that the vendor originally intended helps minimize the amount of recoding needed for a technology insertion project.

Another beneficial technique that can be employed both for software and FPGA IP is to analyze the vendor-supplied APIs and block interfaces to identify those interfaces that are likely to shift in future products and to create an abstraction layer or "shim" between them and the application code. A helpful clue is that if an API or block interface closely mirrors the underlying hardware, it is likely to shift between product generations. While such layers can be seen as adding unnecessary code and performance delays to a system, often the performance impact is minimal while the benefits for a later technology insertion project can be enormous – changing a shim is much easier than changing multiple instances of an API call or IP block instantiation. It's important not to overuse this approach, however, as adding shims or abstraction layers complicates designs and can sometimes make debugging more difficult.

#### Planning for the future

Technology insertion can live up to its promise of future-proofing, but only if it is adequately planned for up front. Most COTS vendors have developed successive generations of products with this in mind. In order to capture this value, system integrators need to work closely with such vendors early in the design cycle.

Mark Littlefield is product marketing manager for Curtiss-Wright Controls Embedded Computing's FPGA computing products. He has more than 15 years of experience in the embedded computing industry, first as an engineer developing

robot vision systems for NASA, then later as a field applications engineer, technical program manager, and product manager. Mark has a BS and an MS in Control Systems Engineering from the University of West Florida.

#### **Curtiss-Wright Controls Embedded Computing**

741-G Miller Drive SE Leesburg, VA 20175 703-779-7800 mark.littlefield@curtisswright.com www.cwcembedded.com

Manuel Uhm is senior marketing manager for the DSP division at Xilinx, responsible for strategic marketing and development of division road maps for commercial wireless and defense. Prior to joining Xilinx in 2004, Manuel was responsible

for marketing at Spectrum Signal Processing, Inc. He is currently co-chair of the markets committee of the SDR Forum. Manuel received his MBA from Simon Fraser University and studied Electrical Engineering at Queen's University.

#### Xilinx, Inc.

2100 Logic Drive San Jose, CA 95124 408-559-7778 manuel.uhm@xilinx.com www.xilinx.com

# **EXPERIENCE**

25 Years of MIL-STD-1553 Service!

Toll Free: 1-800-DDC-5757

www.ddc-web.com

# Trends in SDR and reconfigurable computing

# Configurable PMCs put an FPGA to work

By Jeff Biviano and Dave Barker

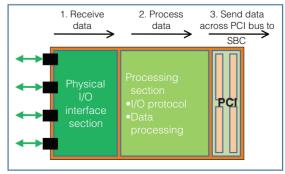

Reconfigurable computing isn't a novel concept, but the idea of a configurable PMC using an FPGA, swappable I/O adapter modules, and I/O-specific IP is a new wrinkle. These configurable PMCs can help reduce design time by providing a platform for adding I/O to a single board computer with PMC sites. We explore the key architectural points to consider in designing around the configurable PMC concept.

It's natural for engineers to spend much of their time thinking about the core processing capability of a system, often in the form of a single board computer. However, experienced designers know that getting the most out of a system means devoting much of their attention to I/O capability, especially in the case of high-speed I/O.

Perhaps a custom sensor for a surveillance system must be integrated, but a full custom I/O design is time prohibitive. Or, perhaps a C4ISR module requires increased A/D performance, but again a totally new A/D design would take too long. In both cases, the developers probably have other development and integration issues to address and don't have the time or resources to devote to developing new I/O cards.

Modular I/O subsystems designed around an FPGA can make a developer's life easier by reusing common components and tailoring the solution to fit application needs. An I/O subsystem can be based on any form factor, but there is strong argument for basing it on the industry-standard PMC form factor. According to Venture Development Corporation, 88 percent of single board computers sold in 2007 are projected to have PMC or XMC sites available. This is because of the success of the proven PMC form factor over its decade-plus life.

#### **Architecture for configurable PMCs**

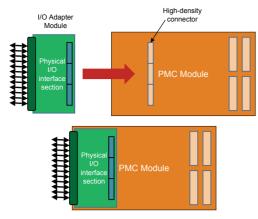

Configuring a PMC for a variety of I/O roles logically involves three architectural elements (Figure 1):

- Adapting the I/O pinout to meet the physical interface requirement

- Providing the I/O data acquisition and processing functionality

- Setting data from the PMC into the host single board computer for further processing

#### Adapting the I/O pinout

To satisfy the needs of a different application or the changing requirements of the same application, a new PMC has to be built. However, if the PMC is designed from the start with an FPGA and the I/O interface is on a pluggable I/O adapter module, the only portion of the hardware that needs to be changed is the pluggable I/O adapter module (Figure 2); the base PMC module can be reused with the appropriate programming of the FPGA.

This modular approach has the advantage of flexibility to adapt a wide variety of I/O types with a single hardware architecture and the ability to evolve with changing requirements over time. It also cuts development cycle times since proven and optimized functional blocks such as

memory interfaces and PCI/PCI-X connectivity are reused.

Pluggable I/O adapter modules can be designed for a variety of I/O functions; with an open interface, the possibility exists for custom user-designed I/O adapter modules for even more functions. These modules can contain both the necessary physical elements and funct-

ional circuitry such as a high-speed A/D converter to capture data from an I/O device. For instance, an I/O adapter module with dual 16-bit 125 MSps A/D channels operating simultaneously will produce 500 MBps of data. A PMC-X module with a 133 MHz 64-bit PCI-X link with approximately 1 GBps bandwidth is able to support these data rates.

### I/O data acquisition and processing functionality

An FPGA on the PMC provides the developer with the flexibility of not only implementing the necessary I/O protocol but also the ability to implement applicationspecific processing and the performance to process very high data rates in real time. Building on the previous A/D example, if the application required two additional analog input channels, a quad 16-bit 125 MSps A/D I/O adapter module could be developed that would produce 1 GBps of data. This would most likely exceed the theoretical ~1 GBps of 133 MHz 64-bit PCI-X. However, if only a 5 MHz band of interest was desired in each channel, a digital down converter could be used to produce a downconverted sample rate of 12.5 MHz based on a sampling frequency of 2.5 times the 5 MHz bandwidth. The data coming out of the FPGA would be reduced to 100 MBps (12.5 MHz/sec x 16-bits/

Figure 1

Figure 2

sample x 4 channels), which could easily be handled by the PCI-X link.

Another way to handle higher input data rates is to increase the capacity of the link between the PMC and the single board computer. PMC-X and XMC modules can increase the bandwidth over the 64-bit, 66 MHz PCI link of a PMC.

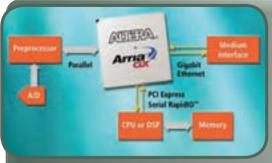

#### Data movement into host SBC

A PCI, PCI Express, Serial RapidIO, or PCI-X interface can be implemented with an ASIC. Alternatively, these capabilities can be implemented as an IP core in the FPGA. By choosing the right FPGA, a single FPGA can interface to the I/O, implement the protocol and preprocess the data, and include a PCI, PCI-X, Serial RapidIO, or PCI Express IP core to interface the PMC/XMC to the single board computer. With the host interface logic implemented in an FPGA, system throughput can be optimized by attention to elements such as buffering, interrupt handling, DMA, and other strategies to help data stream efficiently from the I/O subsystem into the core processing complex.

Utilizing this approach, it's difficult not to envision a single PMC with a family of pluggable I/O adapter modules spanning a range of high-speed functions all based on the same FPGA hardware and IP. An example implementation of this approach is the VMETRO

PMC-FPGA05 family, with a Xilinx Virtex-5 and a series of off-the-shelf I/O adapter modules and IP for I/O including A/D, D/A, FPDP, LVDS, Camera Link, RS-485, and L-band digital receiver functions (Figure 3).

In this implementation, a 138-pin connector near the PMC front panel brings signal traces routed for use as either single-ended signals or differential pairs to the FPGA. The signals are grouped into two banks, with each bank independently configurable to 2.5 V or 3.3 V signaling. Having 138 configurable pins routed from an FPGA to an I/O adapter module connector provides the capability to support a wide range of I/O.

#### Configuring the FPGA

The ideal configurable FPGA platform provides a flexible I/O module interface that can be used to accommodate a multitude of I/O functions from analog conversion to interfacing with complex bus protocols. However, the primary focus for an application is the core processing algorithm. To allow application engineers to concentrate their efforts on the design of the algorithm, it is imperative that they have accompanying interface IP at their disposal. The IP needs to abstract away the intricacies of complex protocols, providing simple intuitive interfaces that can be easily integrated with the core processing algorithm.

Figure 3

Interface IP can typically be broken down into two basic categories:

- Streaming interfaces where a continuous data stream is presented

- » Addressable interfaces where data is stored or retrieved from a specified location

Providing a common method for interfacing to these two categories of interfaces allows an array of I/O options to be readily adapted to by an application programmer.

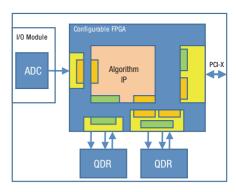

A look at the block diagram of the example implementation highlights three interfaces that are commonly present in a configurable FPGA platform (Figure 4).

#### I/O module interface

The I/O module interface most often represents sensor input and arrives in a streaming format. In the example block diagram, the I/O is a single channel of ADC input data. The associated IP interface takes the ADC samples and presents

the user with a common streaming IP interface that can connect directly to the processing algorithm block or can be connected to FIFO with a compatible interface for crossing between the operating frequency of the ADC interface to the algorithm interface.

#### Memory interfaces

Memory interfaces typically addressable in nature, but in some instances memory can be used to buffer a data stream. The example implementation shows two blocks of external memory with two associated styles of IP blocks. The first block provides user interfaces that can be used to address individual memory elements such as where memory is being used as a lookup table for a processing algorithm. The second IP block illustrated shows the memory interfaces with streaming interface blocks for the user to connect an input interface to one and an output to the other. Thus the user has a simple choice to connect the algorithm directly to the PCI-X interface or use the QDR as a buffer that

Figure 4

can absorb data during instances where there is a delay or hiccup in transferring data across PCI-X to a general purpose processor.

#### Common IP interface advantages

By creating a common method for interfacing to IP elements, the user is able to concentrate most of the coding effort on analysis of the different types of filtering and processing effects in the algorithm, as opposed to creating glue logic to interface to the varying bus protocols. Once common interfaces have been established, they can

be utilized by high-level FPGA tools such as Xilinx System Generator or Impulse C. Thus, the high-level tools can be used to create IP that more readily drops into a larger FPGA design.

#### **Drivers and software**

Once the FPGA design is established, it behaves identically to how any "hard" PMC design would. To integrate the configured FPGA platform into the target system, software needs to be established to communicate between the FPGA and the attached general purpose processor.

Platform software should take advantage of reusable IP and provide reusable drivers. As there are variances in the reconfigurable designs such as the number of DMA channels, or the location of register control interfaces connected to the PCI-X interface, the software needs to be able to adapt. One way for the software to automatically adapt to the changes in the hardware interface is to provide a feature table in hardware that can be referenced when the platform drivers are initialized. The combination of the configuration table in hardware and adaptable driver software from a plug-and-play interface can, for instance, dynamically instantiate the corresponding number of DMA drivers in software.

Established software APIs should include support for accessing the addressable interface connected to the PCI-X interface, accessing streaming interfaces connected to the DMA channels, as well as respond to asynchronous interrupt events from the configurable FPGA device.

#### Advanced design tools

High-level design tools are becoming more prevalent in the configurable FPGA industry. The tools abstract away the finite details of HDL languages, allowing designers to create their FPGA algorithms in more familiar and mathematically friendly environments such as The MathWorks Simulink environment and C.

Common IP interfaces aid in integrating such cores into larger designs. In addition, these high-level tools can perform hardware verification of the completed FPGA design by using configurable platform software to send the simulated data sets to real hardware while reading back the processed data results to ensure that the hardware design matches the simulation results.

#### Tapping the power of reuse

We have shown how using configurable PMCs with pluggable I/O adapter modules backed by an FPGA delivers tangible benefits for system designers. Developers can reuse functionality, tailor, or even customize I/O to meet specific needs and offload preprocessing functions using the FPGA's capability. Because of the highly integrated designs that can be achieving utilizing a modular FPGA-based PMC approach, faster, denser systems can be designed with a reduced SWaP footprint. Robust FPGA development and debug toolsets, along with off-the-shelf, proven, optimized IP blocks, help reduce design cycle times. Designing around a configurable PMC, whether developed in-house or a COTS product, is an approach that designers should strongly consider.

Jeff Biviano is a senior systems engineer at VMETRO. He served in a systems engineering role for five years at Transtech

DSP before its acquisition by VMETRO in 2004. Jeff has a BS in Computer Engineering Technology from the Rochester Institute of Technology.

Dave Barker is VP of market development for embedded solutions at VMETRO. Before joining VMETRO in 2005, Dave

was marketing manager for VME products at the Motorola Computer Group and has worked in the industry for more than 25 years. Dave has a BS in Computer Science from the University of Pittsburgh and an MBA from the University of Phoenix.

#### VMETRO, Inc.

1880 Dairy Ashford, Suite 400 Houston, TX 77077 281-584-0728 jbiviano@vmetro.com dbarker@vmetro.com www.ymetro.com

### **In-Vehicle PCs**

smallest dimensions, fanless, high reliability, rugged design

- \_ Intel® Pentium® M 738, 1.4GHz

- \_ VGA, DVI, LVDS, Audio, Video-in

- \_ LAN, COM1, COM2, 4x USB, 2x firewire, Digital I/O

- \_ Exchangeable mediapack 40GB automotive HDD 1x CF TypeII

- Options: UPS-battery, preheating, GSM, GPS, WLAN, CAN

DIGITAL-LOGIC offers a large variety of Embedded Computer in **PC/104**, **EPIC**, **EBX**, **3.5"**, **smartModule** and other form factors.

Further informations:

www.digitallogic.com

DIGITAL-LOGIC

smart embedded computers

# RTD Embedded Technologies, Inc.

"MIL Value for COTS prices"™

Pentium® M cpuModules™

8000 MIPS dspModules™

|             | остано организации                 |                   |                        |                       |                       |                  |                  |                  |                  |                  |                  |                 |                 |                 |   |

|-------------|------------------------------------|-------------------|------------------------|-----------------------|-----------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|---|

|             |                                    |                   | Pentium <sup>®</sup> M |                       |                       | Intel® Celeron®  |                  |                  |                  |                  | AMD Geode        |                 |                 |                 |   |

|             | cpuModules™<br>-40 to +85°C        | CMX158886PX1400HR | CMD158886PX1400HR      | CMX158886PX1400HR-BRG | CMD158886PX1400HR-BRG | CME147786CX400HR | CME147786CX650HR | CML147786CX400HR | CML147786CX650HR | CMX147786CX400HR | CMX147786CX650HR | CME26686CX333HR | CME27686CX333HR | CMC26686CX333HR |   |

|             | AT Expansion Bus                   |                   |                        | ✓                     | ✓                     | ✓                | ✓                | <b>√</b>         | <b>V</b>         | <b>✓</b>         | <b>V</b>         | ✓               | ✓               | ✓               | ĺ |

| Bus         | <b>PCI Universal Expansion Bus</b> | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | 1                | ~                | $\checkmark$     | <b>V</b>         | ✓                |                 | ✓               |                 |   |

| B           | PCI Bus Masters                    | 4                 | 4                      | 4                     | 4                     | 4                | 4                | 4                | 4                | 4                | 4                |                 | 4               |                 |   |

|             | APIC (add'l PCI interrupts)        | 9                 | 9                      | 9                     | 9                     | 9                | 9                | 9                | 9                | 9                | 9                |                 |                 |                 |   |

| and BIOS    | CPU Max Clock Rate (MHz)           | 1400              | 1400                   | 1400                  | 1400                  | 400              | 650              | 400              | 650              | 400              | 650              | 333             | 333             | 333             | Ĺ |

|             | L2 Cache                           | 2MB               | 2MB                    | 2MB                   | 2MB                   | 256k             | 256k             | 256k             | 256k             | 256k             | 256k             | 16K             | 16k             | 16k             |   |

|             | Intel SpeedStep Technology         | ✓                 | ✓ /                    | 1                     | ~                     |                  |                  |                  |                  |                  |                  |                 |                 |                 |   |

|             | ACPI Power Mgmt                    | 2.0               | 2.0                    | 2.0                   | 2.0                   | 1.0              | 1.0              | 1.0              | 1.0              | 1.0              | 1.0              |                 |                 |                 |   |

|             | Max Onboard DRAM (MB)              | 512               | 512                    | 512                   | 512                   | 512              | 512              | 512              | 512              | 512              | 512              | 256             | 256             | 256             |   |

| _a          | RTD Enhanced Flash BIOS            | <b>✓</b>          | 1                      | 1                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                | ✓               | ✓               | ✓               |   |

| CPU         | Nonvolatile Configuration          | 1                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                | ✓               | ✓               | ✓               |   |

|             | <b>Quick Boot Option Installed</b> | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                | ✓               | ✓               | ✓               |   |

|             | USB Boot                           | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                |                 |                 |                 |   |

|             | Watchdog Timer & RTC               | ✓                 | <b>√</b>               | ✓                     | ✓                     | <b>✓</b>         | ✓                | ✓                | ✓                | ✓                | ✓                | <b>✓</b>        | ✓               | ✓               |   |

|             | IDE and Floppy Controllers         | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                | ✓               | ✓               | ✓               |   |

| S           | ATA/IDE Disk Socket, 32 DIP        | 1                 | 1                      | 1                     | 1                     | 1                | 1                | 1                | 1                | 1                | 1                | 1               | 1               | 1               |   |

| Peripherals | Audio                              | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                |                 |                 |                 |   |

| she         | Digital Video                      | LVDS              | LVDS                   | LVDS                  | LVDS                  |                  |                  | TTL              | TTL              | LVDS             | LVDS             | TTL             | TTL             |                 |   |

| eri         | Analog Video                       | SVGA              | SVGA                   | SVGA                  | SVGA                  | SVGA             | SVGA             | SVGA             | SVGA             | SVGA             | SVGA             | SVGA            | SVGA            |                 |   |

| ۵           | AT Keyboard/Utility Port           | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                | ✓               | ✓               | ✓               |   |

|             | PS/2 Mouse                         | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                | ✓               | ✓               | ✓               |   |

|             | USB Mouse/Keyboard                 | ✓                 | ✓                      | ✓                     | ✓                     | ✓                | ✓                | ✓                | ✓                | ✓                | ✓                | ✓               | ✓               | ✓               |   |

| 0/1         | RS-232/422/485 Ports               | 2                 | 1                      | 2                     | 1                     | 2                | 2                | 2                | 2                | 2                | 2                | 2               | 2               | 2               |   |

|             | USB 2.0 Ports                      | 2                 | 4                      | 2                     | 4                     |                  |                  |                  |                  |                  |                  |                 |                 |                 |   |

|             | USB Ports                          |                   |                        |                       |                       | 2                | 2                | 2                | 2                | 2                | 2                | 2               | 2               | 2               |   |

|             |                                    | 1                 |                        | 1                     |                       | 1                | 1                | 1                | 1                | 1                | 1                | 1               | 1               |                 |   |